1.6 KiB

@TOC

1 mem_mcu_wrap top

在这里为了TOP集成的自动化和效率,使用verilog-mode来集成;

1.1 总体功能概述

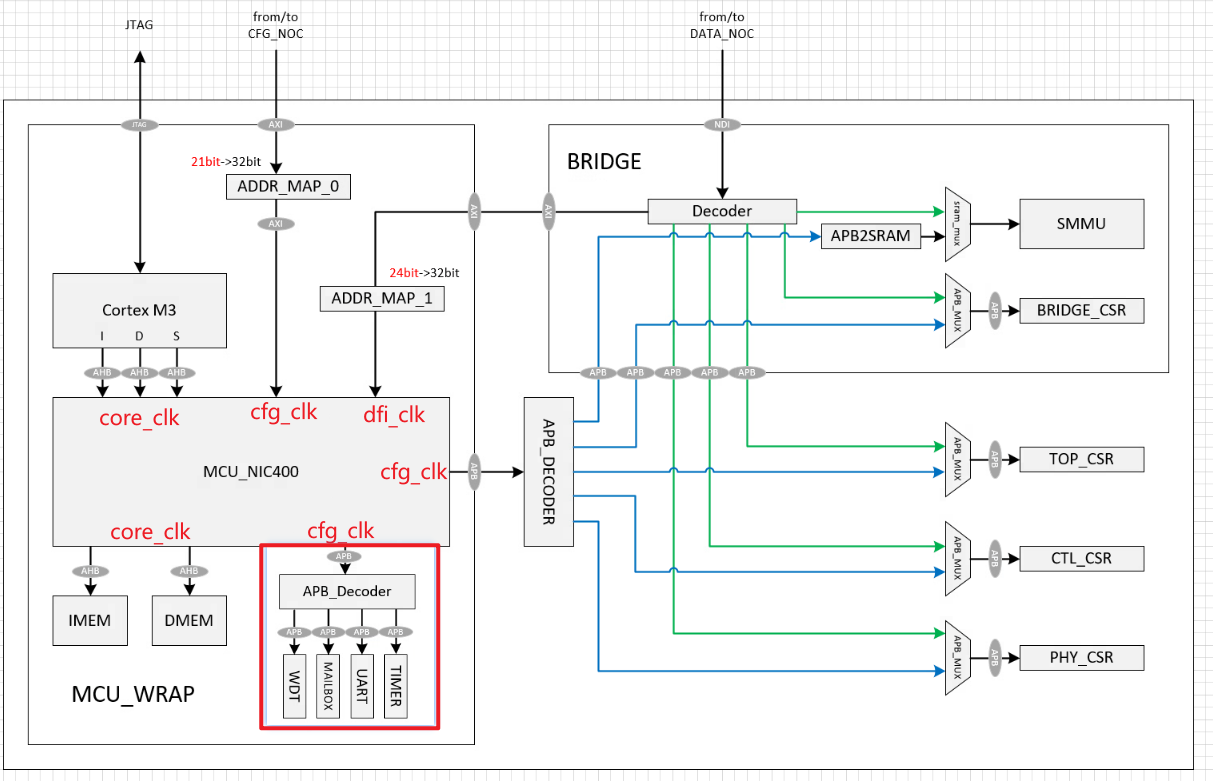

mem_mcu_wrap模块是一个顶层模块,主要负责将Corelink子模块和其他多master、多slave进行集成连接起来,它的主要功能是如下所示:

1.2 总体结构框图

1.3

2 Corelink子模块

2.1 功能概述

该Corelink是由AMBA_de工具生成的nic400 switch模块;

2.2 地址分配

2.3 结构框图

2.4 设计详述

3 记录问题

Verilog-mode使用

1.1 变量范例使用

// Local Variables: // verilog-library-flags:("-y ./") // verilog-auto-inst-param-value:t // verilog-auto-input-ignore-regexp:"" // verilog-auto-output-ignore-regexp:"" // End:

----------------------------------------> // Local Variables: // verilog-library-flags:("-y ./ -y ../common/basic -y ../common/cfg_noc -y ../common/crg -y cortexm3/cortexm3_integration/verilog -y ./nic400_ahb_matrix/nic400/verilog ") // verilog-auto-inst-param-value:t // verilog-auto-input-ignore-regexp:"mcu_intisr \|mcu_core_obs_internalstate_\|cfg_noc_engine.err_info_clear" // verilog-auto-output-ignore-regexp:"mem_ctrl_bus\|cfg_die_crd_\|_info_tmp\|" // End:

1.2 带参数例化使用

带参数的例化是在 (/AUTOINST/)中进行使用

/* sub_block AUTO_TEMPLATE(

.\(.*\) (\1[]),

);

*/

sub_block #(

.PARAM1(PARAM1_VALUE),

.PARAM2(PARAM2_VALUE),

.PARAM3(PARAM3_VALUE)

) u_sub_block( /*AUTOINST*/);