4.7 KiB

@[TOC](apb2axi DS文档)

1 功能概述

本设计模块是面向eth MAC CSR的AXI接口,设计apb2axi_bridge来进行给MAC CSR下发配置,考虑该模块具有一般通用性,可作为后续的通用性;

1.1 MAC IP CSR

- 统一使用AXI总线管理控制信号和状态反馈

- 内置事务超时机制和死锁预防电路

- 集成中断仲裁器,多中断源合并为单输出

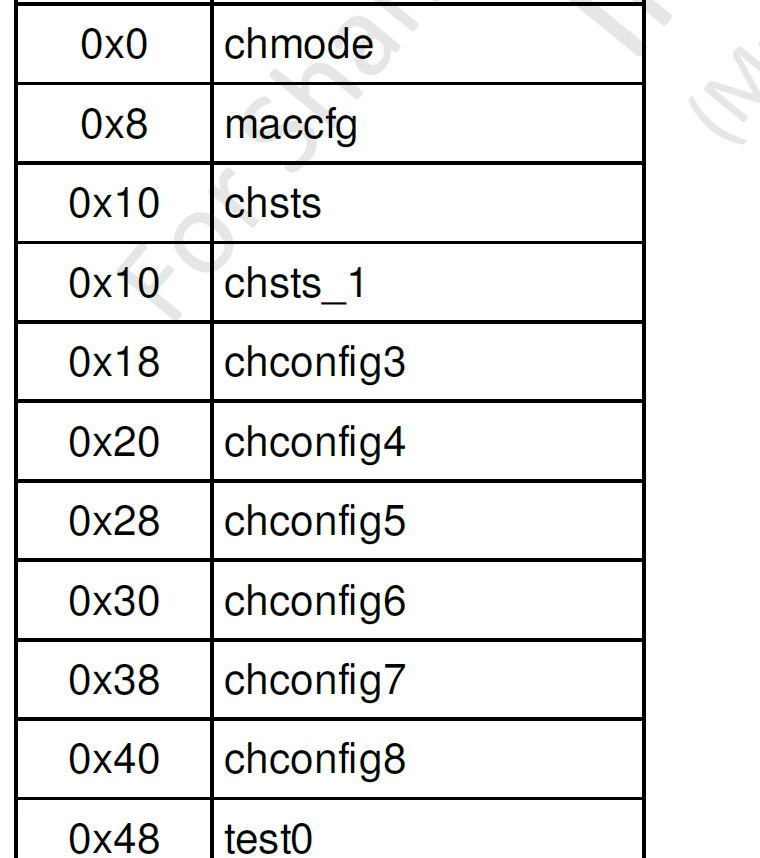

- 各功能通道寄存器采用线性地址映射

- 写1清除(Write-1-to-Clear)中断标志位

- 每个中断源有独立使能寄存器

- 基于功能通道的中断分组机制

2 接口列表及相关时序

2.1 APB

apb相关接口应该是为了保持统一而使用32bit(待确认,因为脚本是支持生成64bit的),apb相关接口时序如下: 信号包括:PCLK, PRESETn, PSEL, PENABLE, PADDR, PWRITE, PWDATA, PRDATA, PREADY, PSLVERR。 传输分为两个阶段:Setup阶段(PSEL=1,PENABLE=0)和Access阶段(PSEL=1,PENABLE=1)。当PREADY=1时,传输完成。

2.2 AXI

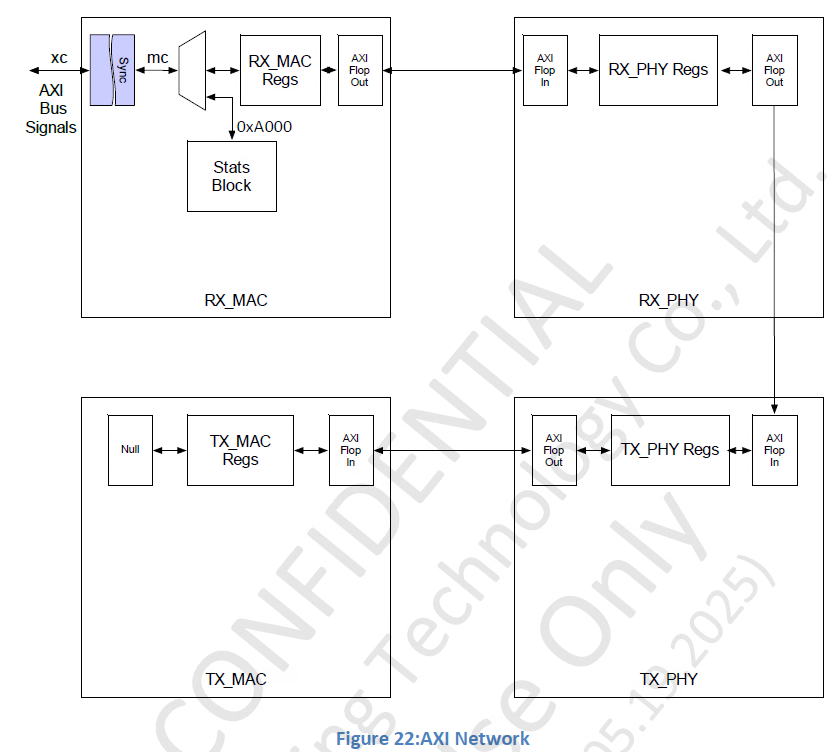

2.2.1 AXI拓扑结构()

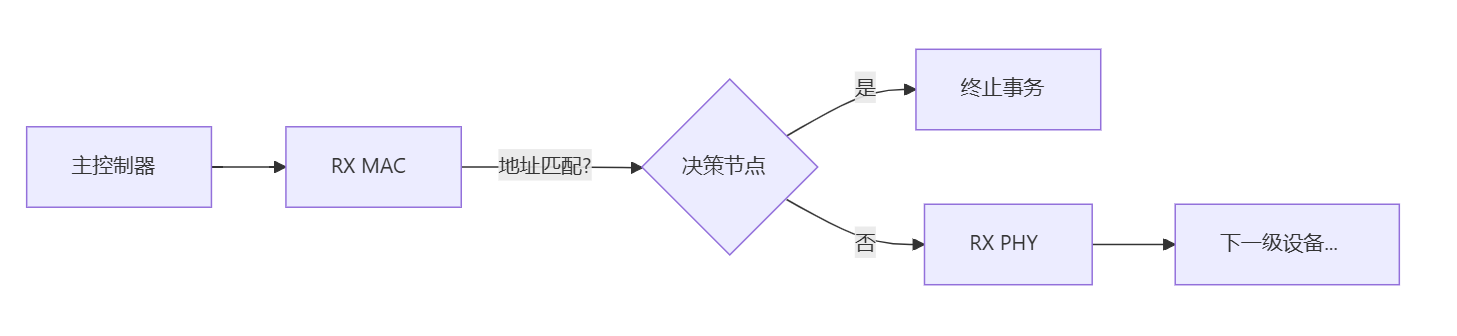

担心是否会在某一个串联的slave挂死--内置超时机制; 伪代码如下:

def handle_transaction(addr):

if (MY_BASE_ADDR <= addr <= MY_END_ADDR): # 地址匹配本模块

process_locally() # 本地处理

return TERMINATED # 终止传递

else:

forward_to_next() # 转发至下一级

return FORWARDED

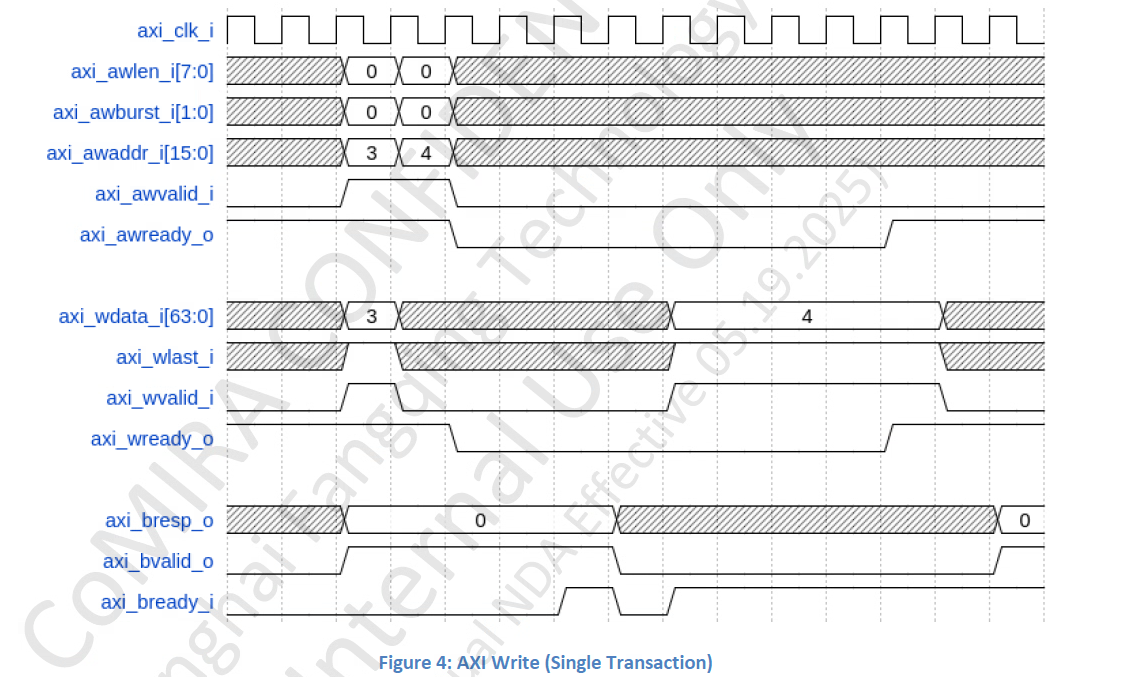

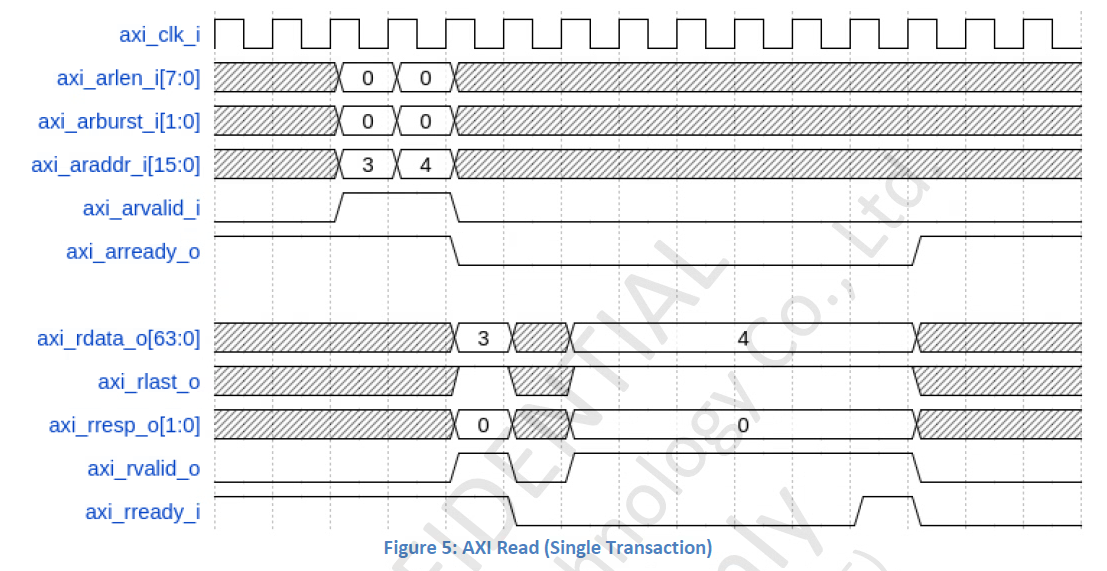

2.2.2 接口时序

2.2.3 AXI features

支持功能如下: 1.基本接口规范:64位总线宽度、支持burst; 2.地址操作:固定地址(同一地址连续写入--填充缓冲区)、递增地址突发(地址自动递增的连续传输--内存拷贝); 3.特殊访问类型;支持非64位对齐的内存操作;支持32bit窄访问;

不支持功能: 1.不支持非对齐访问下或窄访问下或回环下的突发操作; 2.保护访问:不支持特权内存级保护机制; 3.不支持原子读写; 4.严格执行顺序执行、不支持乱序处理; 5.不支持8位/16位窄访问;

2.3 bridge接口时序

该bridge转换接口

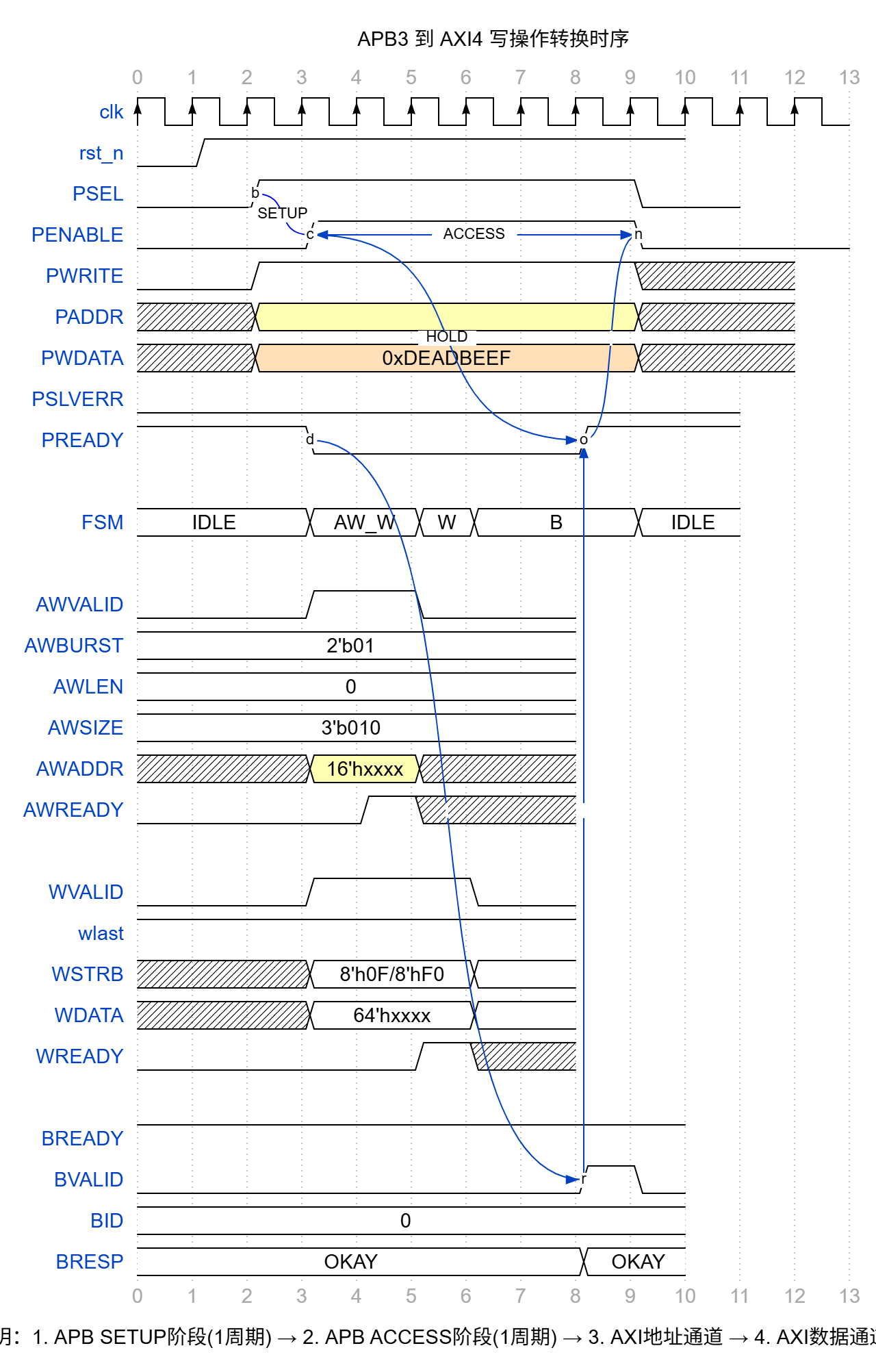

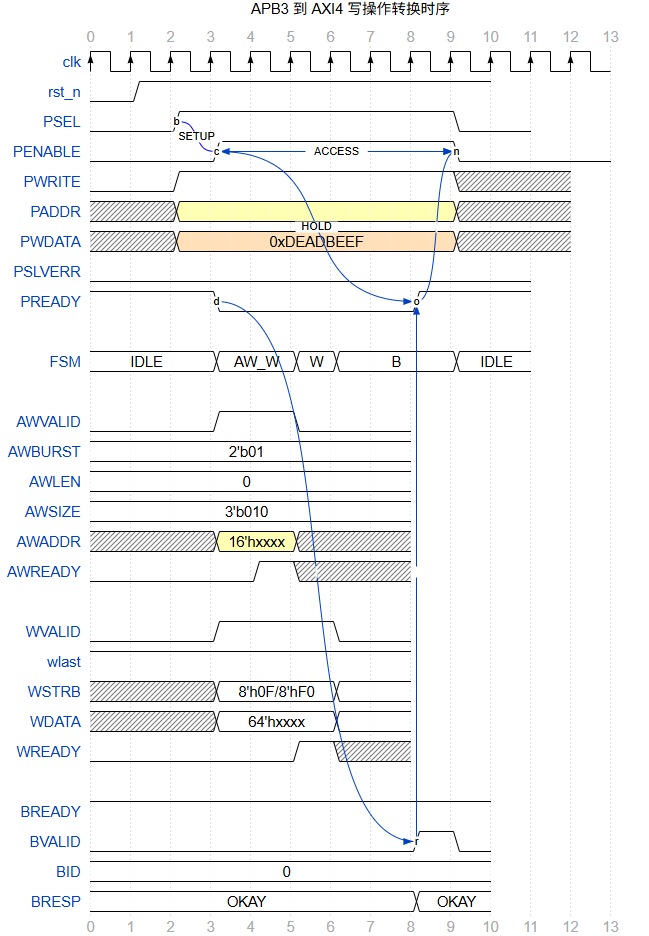

2.3.1 bridge接口写时序

2.3.2 bridge接口读时序

3 模块结构图

4 详细设计

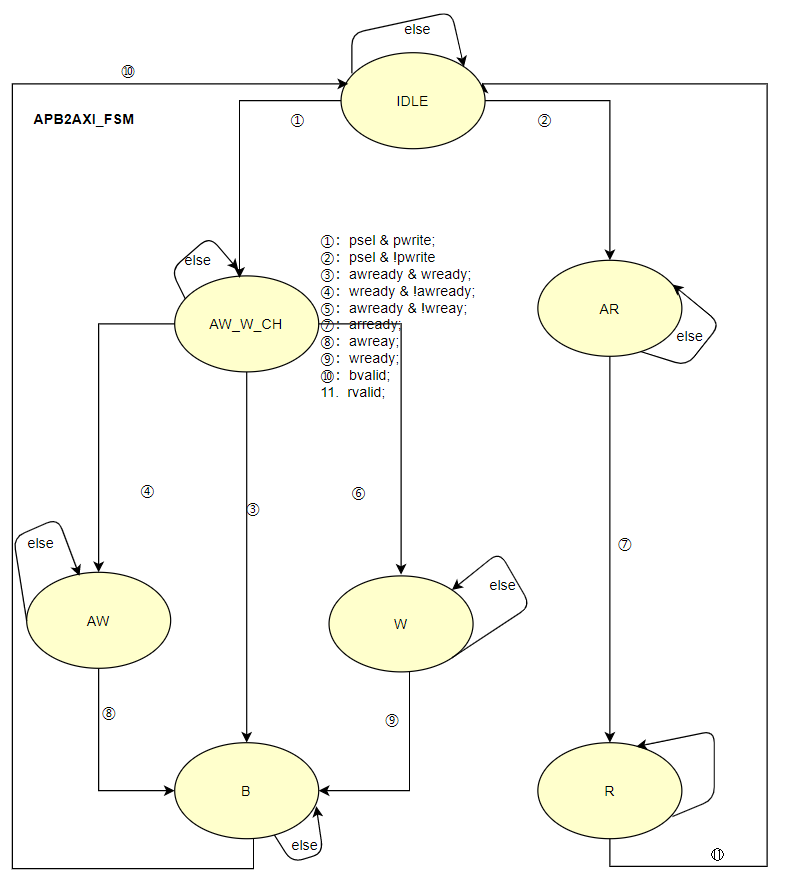

在这里不支持burst和outsanding,每次只处理传输一个APB,因此其转换为AXI4的单个传输(读或写); 寄存器位宽是64bit;相邻寄存器间隔是8;

4.1 读写操作

4.1.1 写操作(32-->64)

APB发起写:设置PADDR, PWDATA, PWRITE=1, PSEL=1,紧接着PENABLE=1。 桥接模块需要将此次写转换到AXI4的写地址通道和写数据通道。 1.先发送写地址(AWVALID=1,等待AWREADY=1); 同时(或之后)发送写数据(WVALID=1,等待WREADY=1) 2.写响应通道:等待BVALID=1,然后桥接模块设置PREADY=1,并传递BRESP(给PSLVERR,0表示OK,1表示错误)。 注意:AXI4的写操作是先发送地址和数据,然后等待响应,而APB是先设置地址和数据,再使能传输。

特别地在这里对于AXI 64bit wdata中通过APB32bit总线配置写,寄存器地址位宽是64bit,连续相邻寄存器地址间隔是8;

在这里AXI地数据位宽是64bit,而APB的总线位宽是32bit,支持窄访问是32bit;

在这里AXI地数据位宽是64bit,而APB的总线位宽是32bit,支持窄访问是32bit;

假如说想配置写0x19f0的64bit; 我理解是:

APB(32位)发起两笔写transaction:

第一笔写低32位:paddr = 0x19f0; pwdata = 32'xx; ----> AXI: awaddr = 0x19f0; wdata = pwdata; wstrb = 8'h0F;wsize = 3'b010;

第二笔写高32位:paddr = 0x19f4; pwdata = 32'xxx; ----> AXI: awaddr = 0x19f4; wdata = pwdata ; wstrb = 8'hF0; wsize = 3'b010;

假如说想配置写0x19f0的64bit; 我理解是:

APB(32位)发起两笔写transaction:

第一笔写低32位:paddr = 0x19f0; pwdata = 32'xx; ----> AXI: awaddr = 0x19f0; wdata = pwdata; wstrb = 8'h0F;wsize = 3'b010;

第二笔写高32位:paddr = 0x19f4; pwdata = 32'xxx; ----> AXI: awaddr = 0x19f4; wdata = pwdata ; wstrb = 8'hF0; wsize = 3'b010;

4.1.2 读操作

APB发起读:设置PADDR, PWRITE=0, PSEL=1,紧接着PENABLE=1。 1.桥接模块将读地址发送到AXI4的读地址通道(ARVALID=1,等待ARREADY=1)。 2.等待读数据通道返回(RVALID=1),然后读取数据,传递给PRDATA,并设置PREADY=1,同时传递RRESP(给PSLVERR)。

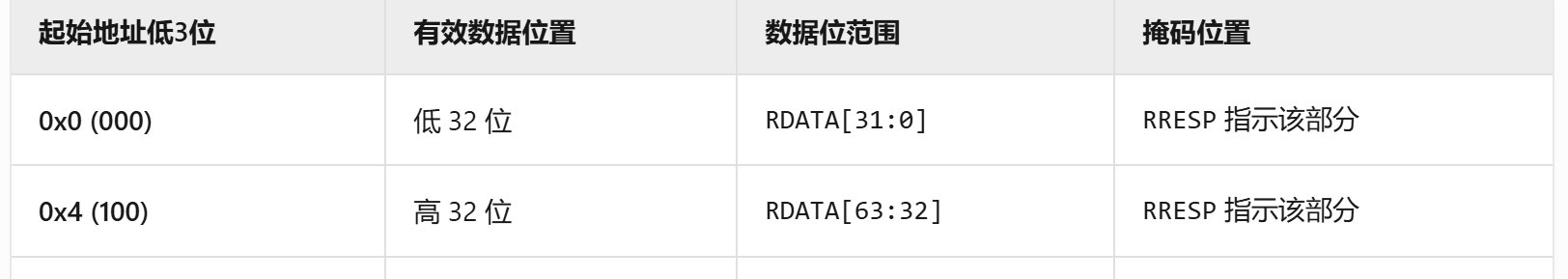

特别地在这里进行对于AXI 64bit中 rdata访问获取32bit;

假如说想配置读0x19f0的64bit; 我理解是:

APB(32位)发起两笔读transaction:

第一笔写低32位:paddr = 0x19f0; ; ----> AXI: awaddr = 0x19f0; prdata = (paddr[2]) ? rdata[64 -1:32] : [32 -1:0];

第二笔写高32位:paddr = 0x19f4; ; ----> AXI: awaddr = 0x19f4;prdata = (paddr[2]) ? rdata[64 -1:32] : [32 -1:0] ;

假如说想配置读0x19f0的64bit; 我理解是:

APB(32位)发起两笔读transaction:

第一笔写低32位:paddr = 0x19f0; ; ----> AXI: awaddr = 0x19f0; prdata = (paddr[2]) ? rdata[64 -1:32] : [32 -1:0];

第二笔写高32位:paddr = 0x19f4; ; ----> AXI: awaddr = 0x19f4;prdata = (paddr[2]) ? rdata[64 -1:32] : [32 -1:0] ;